硅光子学引发全新测试挑战

半导体芯片的持续进步推动着技术与创新的飞跃。如今,这些成果已广泛应用于数据中心AI高性能计算、边缘AI设备、电动汽车、自动驾驶、手机等领域。最新技术创新包括埃米级半导体工艺节点、高带宽内存、先进2.5D/3D异构集成封装、芯粒和裸片间互连等。此外,采用共封装光学(CPO)形式的硅光子技术,将有望成为高性能计算应用中高速数据通信的关键使能技术。

什么是共封装光学?

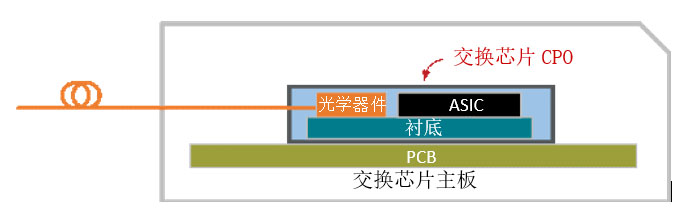

共封装光学(CPO)是一项封装创新技术,将硅光子芯片与数据中心交换机或GPU计算芯片集成到同一衬底上(见图1)。 该技术能够提高数据传输的带宽和速度,降低延迟和功耗,并提升效率,从而满足AI数据中心应用对高性能互连技术日益增长的需求。

要理解CPO,需要先清楚其技术构成。其中,硅光子技术便是CPO的一项关键技术。该技术提供了在硅芯片中直接集成高速光学功能的技术基础。CMOS代工厂已经基于硅半导体技术开发出先进工艺,可在硅晶圆上实现光子功能。CPO采用异构集成封装(HIP),将硅光子芯片与电子芯片(如AI加速器芯片或交换芯片ASIC)直接集成在同一衬底或封装上。 硅光子技术与异构集成封装的结合,促成了CPO产品的诞生。 因此,CPO是硅光子技术、ASIC以及先进异构封装能力供应链的融合成果。

如前所述,CPO为计算核心场景带来了高速、高带宽、低延迟、低功耗的光子互连技术。此外,光子器件在长距离传输中几乎无损耗,这使得一个AI加速器能够与数百米外的另一个AI加速器共同分担工作负载,同时又能作为单一计算资源运行。这种高速长距离的CPO互连结构有望重塑数据中心架构,是解锁未来AI应用的关键创新。

截至2025年,早期CPO原型正在开发中,其将光子“引擎”与交换芯片或GPU ASIC集成在同一衬底上,而非通过先进异构封装实现集成。 此处的光学“引擎”是指将硅光子芯片、其他分立元器件与光纤连接器集成的封装体;而此处的CPO则是指将多个光学引擎与交换芯片或GPU ASIC组装在同一衬底上的技术方案。

如何缩短CPO上市时间?

相较于硅光子制造供应链的传统服务领域,例如电信和生物技术行业的多品种、小批量产品及应用,CPO在数据通信市场的潜在规模要高出约两个数量级。要在如此大规模下成功实现CPO技术,需要同步推进三大关键要素:

- 扩大硅光子供应链产能,并在晶圆和光学引擎层面实现高良率。

- 需与OSAT及合同制造商合作,验证适用于共封装光学的新型异构集成封装方案。

- 开发并验证新的大规模测试技术,替代目前高度依赖人工、无法适配大批量制造的硅光子测试流程。

CPO技术目前尚未成熟,也未进入规模化量产阶段,但测试设备提供商与芯片厂商必须提前布局应对,因其将直接影响从晶圆级、封装级到系统级的自动测试设备需求。为开发能适应光子技术快速发展,并能同时处理电信号和光信号的混合测试系统,加大对光子测试能力的投入至关重要。 CPO测试需要具备以下关键能力:主动热管理、高功率处理、大尺寸封装操作、定制光子器件操作和对准、高速数字信号测试、宽频带光子信号测试及高频RF信号测试。

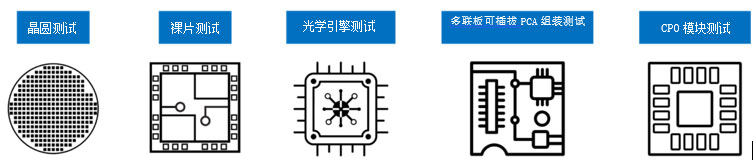

此外,从晶圆测试到最终封装测试存在多道测试环节,均需对测试覆盖率、测试时间和成本方面进行优化(见图2)。需要凭借专业知识和经验优化各环节的测试覆盖率,避免因运营开支和设备投入导致产品制造成本过高。

图2:硅光子技术从晶圆到CPO的测试环节

CPO测试挑战

CPO器件涉及多种电学和光学工艺与材料,因此其测试面临着独特挑战。其中尤为突出的挑战是,为了确保测试结果可靠,必须将光学元件精确对准,而这一过程本身具有复杂性。光信号对微小对准偏差极为敏感,这与连接容差较大的传统电信号截然不同。CPO将光子器件与高数字内容的计算芯片相集成,这种精密结构要求激光器、波导和光电探测器实现精准定位。即使是极细微的对准误差,也可能导致信号衰减、功率损耗或测量失准,从而增加测试过程的复杂性。随着这项技术不断演进,自动测试设备必须不断升级,以满足光子学与光电集成提出的严苛精度要求。

除精度要求外,CPO所采用的材料和工艺也引入了变量。 当来自不同供应商的多个光学芯粒(每个芯粒可能采用不同材料或设计)被集成到同一衬底上时,确保这些异构元件间的对准精度,难度会呈指数级上升。 每个光学芯粒可能都有自己独特的光学特性,这意味着测试设备必须兼容多种光学对准场景,同时确保信号的传输和接收的精度不受影响。这对自动测试设备提出了更高要求,需能够动态适配各类材料与光学设计,并始终保持稳定可靠的测量性能。

此外,实现精确对准的过程非常耗时,大规模半导体测试的效率因此受到严重制约。光学元器件的对准多依赖手动或半自动操作,导致测试周期延长,进而对生产环境的产能和效率造成不利影响。为减少这些延迟,自动测试设备供应商必须投资研发先进的光子测试技术,例如可同时高效处理电信号和光信号的混合系统。此类系统还必须采用更快、更可靠的对准技术,或可借助AI驱动的校准技术与自适应算法实现实时调整。

通过测试满足CPO技术的严苛要求

为支持PCIe 5.0/6.0/7.0和400G/800G/1.6T b/s以太网等最新行业协议,行业对数据互连提速提出迫切需求,数据中心的可靠性和性能都面临着极高的要求。数据互连一旦出现故障或性能不足,可能引发严重的系统停机和性能瓶颈。因此,业界正着力提升测试覆盖率,力求在元器件部署到数据中心前发现并解决潜在问题。这要求半导体测试行业提供全方位的测试解决方案,涵盖元器件性能的各个方面,包括不同工作条件下的信号完整性、热行为和功耗。

最终,行业向CPO的转型将推动测试方法与设备的全面革新,尤其需要确保从晶圆到CPO封装的所有测试环节,都能实现精确的光学对准。那些投资先进光子测试系统的半导体测试领军企业,将更有能力应对这一新兴技术的复杂性,从而跟上技术快速迭代的步伐并满足持续增长的市场需求。

泰瑞达始终站在创新的前沿,洞察新兴技术趋势,并通过主动布局灵活高效的自动测试设备能力,为半导体封装与材料科学的最新突破提供解决方案。